V.4.0, 2016

# SOC MPEG-2 Video Encoder Datasheet

System-On-Chip (SOC) Technologies

### 1. Product Overview

The SOC MPEG2 video encoder IP core is a single chip solution that supports single or multistream MPEG-2 video encoding for all industrial standard resolutions including QVGA, SD and HD up to 1080p/60fps. The encoder encodes either 4:2:0 or 4:2:2 streams whichever is desirable.

SOC provides the versions of the MPEG-2 video encoder IP core for FPGAs of Xilinx, Altera, and Microsemi. SOC also supplies all-in-one encoder modules based on the same H.264 video encoder IP core. Refer to the Product Brief and Datasheet for SOC MPEG codec modules for details.

The SOC MPEG-2 video encoder is implemented based on SOC's proprietary single-clock driven all-hardware technology (without microprocessors or embedded software), which has significant advantages of high-speed (low latency), small footprint (low power), high video quality, and high resolution. The encoder can fit into a low-end FPGA, for example, the low end Xilinx Spartan-6 series, such as the XC6SLX150 and the XC7A200T.

The SOC MPEG-2 video encoder comes with a user API which allows the user to control the operations of the encoder, including CBR or VBR, bit rate, etc. The API user manual is shipped with the evaluation and product development kit.

The SOC encoder series can be integrated with an audio encoder to provide an all-in-one encoding solution. SOC also integrates network modules, TCP/UDP-IP, Ethernet MACs, as well as the MPEG transport multiplexer into the design to produce full system-on-chip systems. Customized versions of these products are available on request.

### 2. The SOC MPEG-2 Video Encoder Architecture

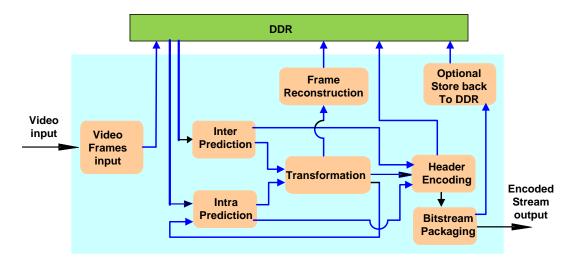

Fig. 1 is the block diagram of the SOC MPEG-2 video encoder. It is a self-contained FPGA IP core that can be either placed into a single FPGA or integrated with other logic blocks in the same FPGA for system-on-chip solutions.

All of the blocks in the design, shown in Fig. 1, are implemented in hardware without embedded processors or embedded software, which offers high speed, low logic resource consumption, and low power. Input to the encoder is standard raw video stream in 4:2:0, 4:2:2 (or 4:4:4) format. The output of the encoder is MPEG-2 elementary stream. SOC also provides an MPEG transport encoder to allow the output of the encoder to be in the form of MPEG transport streams.

The SOC MPEG-2 video encoder requires two external clock sources, one at 100MHz and the second at the video clock frequency (13.5-148.5MHz). The encoder also requires an external DDR3 (or DDR2) memory of minimum of 256MB for 1080p resolution (for both 30fps and 60fps).

Fig. 1 Block Diagram of SOC MPEG-2 video encoder

V.4.0, 2016

# 3. Technical Specifications

### **Conformance Standard:**

MPEG-2/H.262 (ISO/IEC 13818-2)

### **Chroma Format:**

The SOC MPEG-2 video encoder supports:

- o 4:2:0

- o 4:2:2

- 4:4:4 (on request)

### Precision:

The SOC MPEG-2 video encoder supports:

- o 8 bits

- o 10 bits (MPEG-2 Extension)

### Frame Rate:

The SOC MPEG-2 video encoder supports:

- o 10fps

- o 24fps

- o 25fps

- o 29.97fps

- o 30fps

- o 50fps

- o 59.95fps

- o 60fps

#### **Inter Frames:**

The SOC MPEG-2 video encoder supports:

- o I frame

- P frame

- o B frame

V.4.0, 2016

### Latency:

The SOC MPEG-2 video encoder has very low latency due to its hardware implementation. The encoding engine latency is less 0.25ms from data in to data out. The encoder can buffer 1 complete frame before encoding to compensate any jitters of the input stream, when necessary.

### Bit Rate:

- Constant Bit Rate User controllable through API

- Variable Bit Rate User controllable through API.

The average output bit rate is at 10 Mbps for 1080p@30fps, with very good video quality.

There is no upper limit for bit rate. 100Mbps for 1080p@30 has been tested, but it can go higher.

### Power:

The power consumption is less than 800mw for core only. If the core is mapped for ASIC production, the power consumption will be considerably less.

A summary of these specifications is provided in Table-1.

Table-1 Specification Summary Table

| FEATURE                  | DESCRIPTION                                      |

|--------------------------|--------------------------------------------------|

| MPEG Profile             | High Profile                                     |

| Resolution               | QVGA, SD, and HD up to 1080p @30 or 60fps        |

| Frame Rate               | 10, 24, 25, 29.97, 30, 50, 59.95, 60 frames/Sec. |

| Output bit rate          | 5 - 100 Mbps for 1080p@30fps                     |

| Latency                  | 0.25ms (min.)                                    |

| Power                    | < 800mw (on Xilinx Spartan-6 FPGAs)              |

| Interlace Stream         | Support                                          |

| Multiple Channels        | on Artix-7, Kintex-7 K325, Stratix-V             |

| Integrated Audio Encoder | Available                                        |

| MPEG Transport Mux       | Available                                        |

| Ethernet MAC             | Available for integration                        |

| UDP/IP                   | Available for integration                        |

| User defined I/O         | Supported                                        |

V.4.0, 2016

# 4. Targeted FPGAs

The SOC MPEG-2 video encoder fits most of the Xilinx FPGAs, including:

- Virtex-5

- o Spartan-6

- o Virtex-6

- o Kitex-7

- o Virtex-7

- o Artix-7

- o Zynq-7.

Encoder IP cores are also available for Altera FPGAs, including:

- o Cyclone- V

- o Arria-V

- o Arria 10

- Stratix-IV and V

### **Logic Resources on Xilinx FPGAs:**

The logic resources required on Xilinx FPGAs by MPEG-2 encoder IP core is listed in Table-1

| Resources type | Resource Utilization |  |

|----------------|----------------------|--|

| LUTs           | 90k                  |  |

| Logic cells    | 170k                 |  |

| B-RAM 7Mbits   |                      |  |

| DSPs 320       |                      |  |

Table-1 Logic resource utilization

### Logic Resources on Altera FPGAs:

The logic resources required on Altera FPGAs by the MPEG-2 encoder IP core is listed in Table-2

| Resources type | Resource Utilization |  |

|----------------|----------------------|--|

| ALM            | 60k                  |  |

| B-RAM          | 5Mbits               |  |

| DSPs           | 310                  |  |

Table-2 Logic resource utilization

V.4.0, 2016

# 5. Applications

- Video surveillance cameras;

- Video conferencing devices;

- Digital cinemas;

- Smart cell phones;

- Consumer products;

- Cable TV headend;

- IPTVs distributing;

- Satellite video/audio transmission equipment;

- Broadcast Equipment;

- Medical imaging devices.

### 6. Use the SOC MPEG-2 Video Encoder

SOC provides three formats to customers, which allows for ease-of-use of the product. These formats include:

- 1. FPGA IP cores

- Self-contained IP cores for FPGA users.

### 2. SOC MPEG Codec Modules

SOC provides all its codecs on small circuit boards that integrates all required components for video, audio or both video and audio encoding. The codec module connects to a host device via a PCB connector. SOC also provides evaluation/development boards for the modules and IP cores.

- 3. Customized system-on-chip solutions surrounding the encoder

- SOC provides integration with other IP cores to produce a system-on-chip solution.

Technical data for using each of the above formats are described in the following sub-sections.

V.4.0, 2016

# 7. The MPEG-2 Video Encoder Integration Sheet

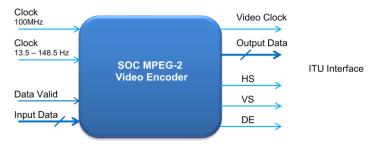

When the encoder is delivered in IP core format, it is a ready-to-use bit-stream core for FPGAs. Fig. 2 shows the inputs and outputs of the encoder core.

The MPEG-2 video encoder IP core integration details are provided in a separate document under the title of "MPEG-2 Video Encoder IP Core Integration Sheet".

Fig. 2 The inputs and outputs of the MPEG-2 video encoder IP Core

### 8. The SOC MPEG Code Modules

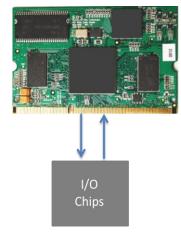

SOC supplies all its MPEG2 and MPEG4-AVC/H.264 encoders and decoders on a 2.7"x1.7" or 2.7x2.0 module (card), as shown in Fig. 3. The modules provide complete function of video/audio encoding or decoding. The module connects to the host product/PCB via a device-to-PCB connector, as shown in Fig. 4.

Fig. 3. SOC MPEG Codec Module

Fig. 4. Device-to-PCB connectors

The SOC MPEG Codec Modules can be directly connected to I/O interface chips for product fabrication, as shown in Fig. 5, or connected to an FPGA or a Microcontroller for user system integrations, as shown in Fig. 6.

Fig. 5 SOC MPEG Codec Module directly connects to I/O interfaces in user product

Fig. 6 SOC MPEG Codec Module connects to FPGA/microcontroller for user integration

Refer to the Product Brief and Datasheet of SOC MPEG Codec Modules for technical details.

# 9. Customized Solutions Surrounding the MPEG-2 Encoder

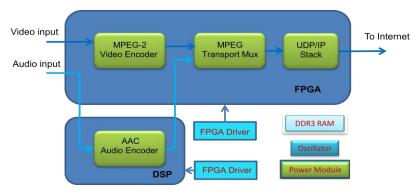

SOC also provides customized system-on-chip integrations based on the MPEG-2 video/audio encoders. Fig. 7 shows an example of an integrated encoder solution for HD video over the Internet with HDMI input.

Fig. 7 Example system-on-chip solution - HD-over-IP encoder

V.4.0, 2016

### 10. User API

The encoder (IP core or module) is controllable through a user API, which allows the user to control the operations of the encoder through setting the registers at runtime. Refer to the "MPEG Video/Audio Encoder API Manual" details.

### 11. Technical Support

SOC provides technical support for all its products, which include documentation, e-mail based, and telephone based support. Additional support services, such as on-site training services, can be subscribed from SOC as a service contract.

### 12. IP core upgrading

Upgrades to the IP core are available to all the delivery formats discussed in Sections 6. Upgrade is usually a part of the technical support contract signed individually. On-line automatic upgrading can also be arranged if desirable.

### 13. Related Information

The SOC MPEG-2 and MPEG-4/H.264 video decoders were implemented based on the same technology of this MPEG-4/H.264 encoder. Refer to the datasheets of SOC MPEG-2 and MPEG-4/H.264 video decoders for details.

# 14. Ordering Information

The SOC MPEG-2 video/audio encoder IP cores are available for licensing, or one-time fee purchase, or a combination of one-time fee plus reduced royalty payments.

The SOC MPEG-2 video/audio encoder module is a complete solution for video and audio encoding at low cost. It is sold on unit by unit basis.

V.4.0, 2016

SOC also provides integration of the MPEG-2 encoder with other functional IP cores of SOC or customer provided IP cores. A combination of NRE and licensing royalties is normally considered, which is negotiated on case by case basis.

Please contact SOC sales by telephone +1 519 880-8609 or e-mail: <a href="mailto:sales@soctechnologies.com">sales@soctechnologies.com</a>

# 15. Document Revisions

| Version # | Revision Date | Notes          |

|-----------|---------------|----------------|

| V.1.0     | 2008/10/25    | First release  |

| V.1.1     | 2010/06/10    |                |

| V.2.0     | 2012/05/15    | Major revision |

| V.2.1     | 2013/06/10    |                |

| V.3.0     | 2014/02/05    | Major revision |

| V.3.1     | 2015/08/07    |                |

| V.4.0     | 2016/05/16    | Major revision |